|

主动吸收2A持续电流接收器源总线终端高速线性调节器CXTP65160双数据率DDR存储系统中产生终端电压稳压器CXTP65161 CXTP65162 | ||||||||||||||||||||||||||||||||||||

|

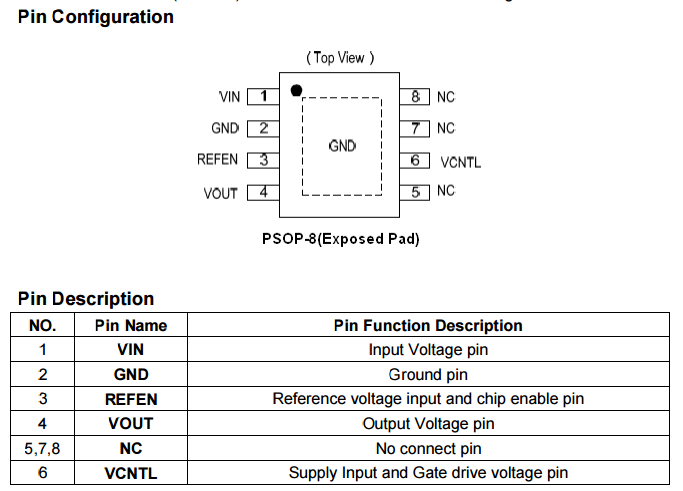

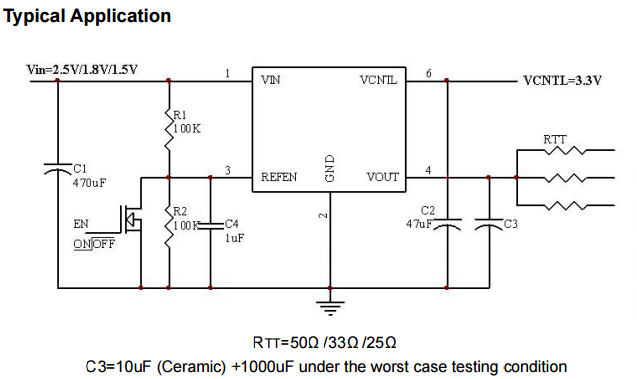

目录7.相关产品 产品概述 返回TOP The CXTP65162 CXTP65161 CXTP65160 is a simple, cost-effective and high-speed linear regulator designed to generate termination voltage in double data rate (DDR) memory system to comply with the JEDEC SSTL_2 and SSTL_18 or other specific interfaces such as HSTL, SCSI-2 and SCSI-3 etc. devices requirements. The regulator is capable of actively sinking or sourcing up to 2A while regulating an output voltage to within 40mV. The output termination voltage cab be tightly regulated to track 1/2VDDQ by two external voltage divider resistors or the desired output voltage can be programmed by externally forcing the REFEN pin voltage. The CXTP65162 CXTP65161 CXTP65160 also incorporates a high-speed differential amplifier to provide ultra-fast response in line/load transient. Other features include extremely low initial offset voltage, excellent load regulation, current limiting in bi-directions and on-chip thermal shut-down protection. The CXTP65162 CXTP65161 CXTP65160 are available in the PSOP-8 (Exposed Pad) surface mount packages.产品特点 返回TOP Ideal for DDR-I, DDR-II and DDR-III VTT Applications Sink and Source 2A Continuous Current Integrated Power MOSFETs Generates Termination Voltage for SSTL_2, SSTL _18, HSTL, SCSI-2 and SCSI-3 Interfaces. High Accuracy Output Voltage at Full-Load Output Voltage traces REFEN Pin Voltage. Low External Component Count Shutdown for Suspend to RAM (STR) Functionality with High-Impedance Output Current Limiting Protection Thermal Shutdown Protection PSOP-8 with exposed pad Pb-Free Package. 应用范围 返回TOP Desktop PCs, Notebooks, and Workstations Graphics Card Memory Termination Set Top Boxes, Digital TVs, Printers Embedded Systems Active Termination Buses DDR-I, DDR-II and DDR-III Memory Systems 技术规格书(产品PDF) 返回TOP 需要详细的PDF规格书请扫一扫微信联系我们,还可以获得免费样品以及技术支持! 产品封装图 返回TOP

电路原理图 返回TOP

相关芯片选择指南 返回TOP 更多同类产品......

发表评论

| ||||||||||||||||||||||||||||||||||||

发表时间:2020-06-29浏览次数:334

| 最新信息 |

|---|

| 热门信息 |

|---|

| 推荐信息 |

|---|

| 头条信息 |

|---|